# SHARP

### Microcomputer Data Sheet

# 4-Bit Single-Chip Microcomputer

#### FEATURES

- 4,096 × 8-bits ROM Capacity

- 160 × 4-bits RAM Capacity (Including 32 × 4-bits Display RAM)

- 98 Instruction Sets

- A RAM Area is Used as Stack Area

- I/O Ports

- 4 Input

- 11 Input/Output plus 15 also used as LCD Segment Port)

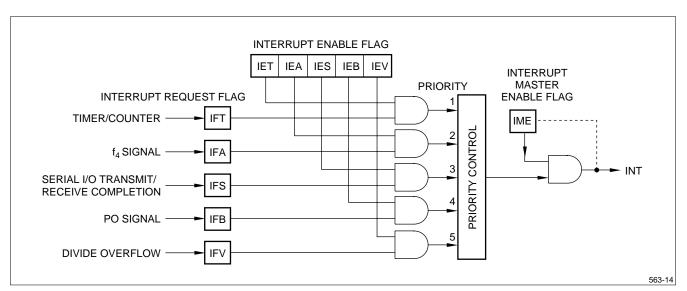

- Interrupts

- Internal Interrupt × 4 (Timer/Counter, f4 Signal, Serial I/O, Divider Overflow)

- External Interrupt × 1 (P0 Signal)

- Timer/Counter 8-bits × 1

- Serial Interface 8-bits × 1

- Built-in Main Clock Oscillator for System Clock

- Built-in Sub Clock Oscillator for Real Time Clock

- Built-in 15 Stages Divider for Real Time Clock

- Built-in LCD Driver

- 128 Segments

- 1/3 Bias

- 1/4 Duty Cycle (If LCD Drive CIrcuit is Used, a Crystal Oscillator Circuit Needs to be Constituted Between OSC<sub>IN</sub> and OSC<sub>OUT</sub>)

- Instruction Cycle Time

- 6.67 µs (TYP., 600 Hz at 3 V)

- 2 μs (MIN., 2 MHz at 5 V)

- Buzzer Output

- Standby Function

- Supply Voltage 2.7 V to 5.5 V

- 64-pin QFP (QFP064-P-1420) Package

#### DESCRIPTION

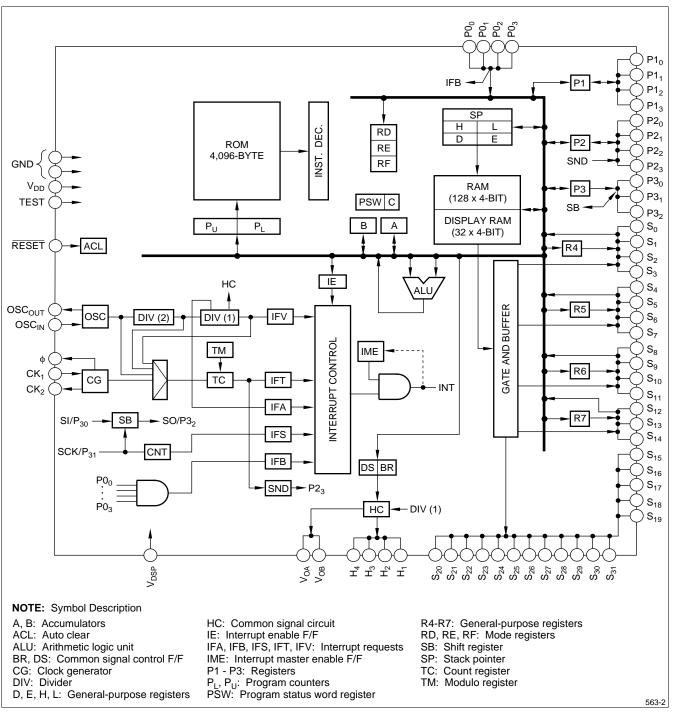

The SM563 is a CMOS 4-bit single-chip microcomputer incorporating 4-bit parallel processing function, ROM, RAM, I/O ports, serial interface, and timer/ counter in a single chip.

It provides five kinds of interrupt and subroutine stack function using the RAM area. Provided with a 128 segments LCD drive circuit, this microcomputer is suitable for low power systems with multiple LCD segments.

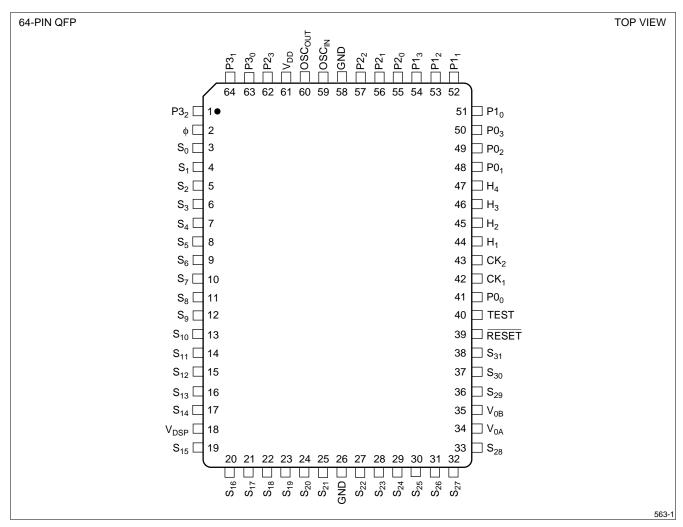

#### **PIN CONNECTIONS**

Figure 1. 64-pin QFP

Figure 2. Block Diagram

#### **PIN DESCRIPTION**

| PIN NAME                                             | I/O      | FUNCTION                                                                                                    |  |

|------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------|--|

| P0 <sub>0</sub> - P0 <sub>3</sub>                    | I        | $A_{CC} \leftarrow P0_0 - P0_3$ , with pull-up resistor                                                     |  |

| P1 <sub>0</sub> - P1 <sub>3</sub>                    | I/O      | I/O selectable by instructions, with pull-up resistor                                                       |  |

| P2 <sub>0</sub> - P2 <sub>3</sub>                    | I/O      | I/O selectable independently, with pull-up resistor. Sound output only when $P2_3$ pin is used as an output |  |

| P3 <sub>0</sub> - P3 <sub>2</sub>                    | I/O      | Serial interface I/O by setting the mode register RE, with pull-up resistor                                 |  |

| S <sub>0</sub> - S <sub>14</sub>                     | O or I/O | Selectable between segment ports and I/O ports through an RC register                                       |  |

| S <sub>15</sub> - S <sub>31</sub>                    | 0        | Display RAM contents output as LCD segment signals                                                          |  |

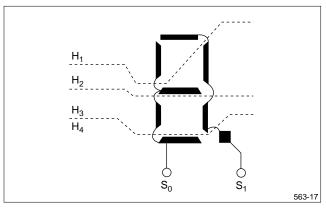

| H <sub>1</sub> - H <sub>4</sub>                      |          | 4-value output capability; used for LCD common output                                                       |  |

| TEST                                                 | I        | For test (connected to GND normally), with pull-down resistor                                               |  |

| RESET                                                | I        | Auto clear, with pull-up resistor                                                                           |  |

| ¢                                                    | 0        | System clock output                                                                                         |  |

| CK <sub>1</sub> , CK <sub>2</sub>                    |          | For system clock oscillation                                                                                |  |

| OSC <sub>IN</sub> , OSC <sub>OUT</sub>               |          | For clock oscillation                                                                                       |  |

| V <sub>DSP</sub> , V <sub>OA</sub> , V <sub>OB</sub> |          | Power supply for LCD driver                                                                                 |  |

| V <sub>DD</sub> , GND                                |          | Power supply for logic circuit                                                                              |  |

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL           | RATING                        | UNIT | NOTE |

|-----------------------|------------------|-------------------------------|------|------|

| Supply Voltage        | V <sub>DD</sub>  | -0.3 to +7                    | V    | 1    |

| Supply Vollage        | V <sub>DSP</sub> | -0.3 to +7                    | V    | 1    |

| Input Voltage         | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    | 1    |

| Output Voltage        | V <sub>OUT</sub> | -0.3 to V <sub>DD</sub> + 0.3 | V    | 1    |

| Output Current        | I <sub>OUT</sub> | 20                            | mA   | 2    |

| Operating Temperature | T <sub>OPR</sub> | -20 to +70                    | °C   |      |

| Storage Temperature   | T <sub>STG</sub> | -55 to +150                   | °C   |      |

#### NOTES:

1. The maximum applicable voltage on any pin with respect to GND.

2. Sum of current from (or flowing into) output pins.

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                     | SYMBOL           | CONDITIONS                       | MIN. | TYP.   | MAX.            | UNIT | NOTE |

|-------------------------------|------------------|----------------------------------|------|--------|-----------------|------|------|

| Supply Voltage                | V <sub>DD</sub>  |                                  | 2.7  |        | 5.5             | V    |      |

| Supply vollage                | V <sub>DSP</sub> |                                  | 2.7  |        | V <sub>DD</sub> | V    |      |

| Basic Oscillation Eroquancy   | f                | $V_{DD}$ = 2.7 V to 5.5 V        | 250  |        | 600             | kHz  | 1    |

| Basic Oscillation Frequency   | I                | V <sub>DD</sub> = 4.5 V to 5.5 V | 250  |        | 2,000           | kHz  | 1    |

| Instruction Cyclo             | t                | $V_{DD}$ = 2.7 V to 5.5 V        | 6.7  |        | 16              | μs   |      |

| Instruction Cycle             |                  | V <sub>DD</sub> = 4.5 V to 5.5 V | 2    |        | 16              | μs   |      |

| Crystal Oscillation Frequency | fosc             |                                  |      | 32.768 |                 | kHz  |      |

#### NOTE:

1. Frequency fluctuation: ±30%.

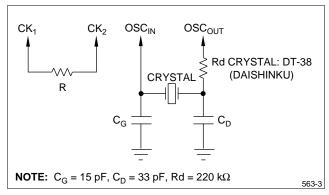

Figure 3. Oscillation Circuit

#### **DC CHARACTERISTICS**

$V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}, \text{ T}_{OPR} = -20^{\circ}\text{C to } +70^{\circ}\text{C}$

| PARAMETER        | SYMBOL           | CONDITIONS                        | MIN.                  | TYP. | MAX.                  | UNIT | NOTE |

|------------------|------------------|-----------------------------------|-----------------------|------|-----------------------|------|------|

|                  | V <sub>IH1</sub> |                                   | 0.7 × V <sub>DD</sub> |      | V <sub>DD</sub>       | V    | 1    |

| Input Voltage    | V <sub>IL1</sub> |                                   | 0                     |      | 0.3 × V <sub>DD</sub> | V    | 1    |

| input voltage    | V <sub>IH2</sub> |                                   | V <sub>DD</sub> – 0.5 |      | V <sub>DD</sub>       | V    | 2    |

|                  | V <sub>IL2</sub> |                                   | 0                     |      | 0.5                   | V    | 2    |

| Input Current    | IIH              | V <sub>IN</sub> = 0 V,            | 2                     |      | 200                   | μΑ   | 1    |

| input ourient    | ΗI               | V <sub>DD</sub> = 4.5 V to 5.5 V  | 20                    |      | 200                   | μΑ   | 1    |

|                  | I <sub>OH1</sub> | $V_{OH} = V_{DD} - 0.5 V$         | 50                    |      |                       | μΑ   | 3    |

|                  | I <sub>OL1</sub> | V <sub>OL</sub> = 0.5 V           | 250                   |      |                       | μA   | 3    |

|                  | I <sub>OH2</sub> | $V_{OH} = V_{DD} - 0.5 V$         | 5                     |      | 250                   | μΑ   | 4    |

| Output Current   | I <sub>OL2</sub> | V <sub>OL</sub> = 0.5 V           | 500                   |      |                       | μA   | 4    |

| Output Current   | I <sub>OH3</sub> | $V_{OH} = V_{DD} - 0.5 V$         | 100                   |      |                       | μΑ   | 5    |

|                  |                  | V <sub>DD</sub> = 4.5 V to 5.5 V  | 400                   |      |                       | μΑ   | 5    |

|                  | I <sub>OL3</sub> | V <sub>OL</sub> = 0.5 V           | 0.5                   |      |                       | mA   | 5    |

|                  |                  | V <sub>DD</sub> = 4.5 V to 5.5 V  | 1.6                   |      |                       | mA   | 5    |

| Output Impedance | R <sub>C</sub>   |                                   |                       | 5    | 20                    | kΩ   | 6    |

|                  | R <sub>S</sub>   |                                   |                       | 10   | 40                    | kΩ   | 7    |

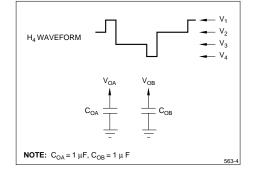

|                  | V <sub>1</sub>   |                                   | 2.7                   |      | 3                     | V    | 8    |

| Output Voltage   | V <sub>2</sub>   | V <sub>DSP</sub> = 3.0 V, No load | 1.7                   | 2    | 2.3                   | V    | 8    |

| Output voltage   | V <sub>3</sub>   | $v_{\rm DSP} = 3.0 v$ , No load   | 0.7                   | 1    | 1.3                   | V    | 8    |

|                  | V <sub>4</sub>   |                                   | 0                     |      | 0.3                   | V    | 8    |

|                  | I <sub>OP</sub>  | f = 600 kHz, $V_{DD}$ = 3.0 V     |                       | 0.4  | 1.5                   | mA   | 9    |

| Supply Current   | L.               | Standby current $V_{DSP}$ = 3.0 V |                       | 15   | 40                    | μA   | 10   |

|                  | I <sub>SB</sub>  | Standby current $V_{DD}$ = 3.0 V  |                       | 8    | 20                    | μA   | 11   |

#### NOTES:

- 1. Applicable pins: P0<sub>0</sub> P0<sub>3</sub>, <u>RESET</u>, P1<sub>0</sub> P1<sub>3</sub>, P2<sub>0</sub> P2<sub>3</sub>, P3<sub>0</sub> P3<sub>2</sub>, (during input mode).

- 2. Applicable pins: CK<sub>1</sub>, TEST, OSC<sub>IN</sub>.

- 3. Applicable pin: CK<sub>2</sub>.

- 4. Applicable pins:  $P1_0 P1_3$  (during output mode).

- 5. Applicable pins:  $P2_0 P2_3$ ,  $P3_0 P3_2$  (during output mode),  $\phi$ .

- 6. Applicable pins:  $H_1 H_4$ .

- 7. Applicable pins:  $S_0 S_{31}$ .

- 8. Applicable pins:  $H_1 H_4$ ,  $S_0 S_{31}$ .

- 9. No load condition.

- 10. No load condition when bleeder resistance is ON.

- 11. No load condition when bleeder resistance is OFF.

#### **PIN FUNCTIONS**

#### GND, V<sub>DD</sub>, V<sub>DSP</sub> (Power Supply Inputs)

Both GND pins 26 and 58 should be grounded. The V<sub>DD</sub> pin is the positive power supply with respect to GND. The V<sub>DSP</sub> is the positive power supply for a LCD driver with respect to GND.

### **TEST (Test Input)**

The TEST pin should be left open or connected to GND with a pull-down resistor.

# **RESET** (Input)

The RESET accepts an active low system reset which initializes the iternal logic of the device. Normally a capacitor of about 0.1  $\mu$ F is connected between this pin and GND to provide a power on reset function.

# OSCIN, OSCOUT (Crystal Oscillator Pins)

The  $OSC_{IN}$  and  $OSC_{OUT}$  pins connect with an external crystal oscillator and these pins and the GND connect with a capacitor, which constitute an oscillator circuit.

The output of the oscillator is coupled to a clock divider for real-time clock operation.

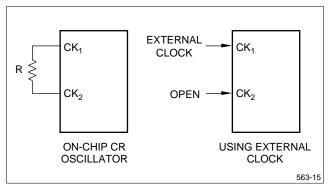

# CK<sub>1</sub>, CK<sub>2</sub> (System Clock CR Oscillator Pins)

The  $CK_1$  and  $CK_2$  pins, in conjunction with a resistor between them, provide a system clock oscillator.

#### H<sub>1</sub> to H<sub>4</sub> (Common Signal Outputs)

The  $\rm H_{1}$  to  $\rm H_{4}$  pins are used to drive the common of a LCD.

#### S<sub>0</sub> to S<sub>31</sub> (Segment Outputs)

The S $_0$  to S $_{31}$  pins drive LCD segments. Pins S $_0$  through S $_{14}$  may also be used as I/O ports when specified with the mode register RC.

#### P0<sub>0</sub> to P0<sub>3</sub> (Inputs)

The P0 pins are normally used to accept key input data. A falling edge at these pins resets the IFB flag.

### P10 to P13 (Input/Output)

The P1 are I/O pins connected to the positive supply with pull-up resistors. They may be switched between input and output modes through an instruction.

#### P20 to P23 (Input/Output)

The  $P2_0$  to  $P2_3$  pins are bit-independent I/O ports which can be independently set to input or output mode with the mode register RF.

When the  $P2_3$  is used for an output pin, it serves exclusively as a sound output pin, which can output a sound signal with any frequency set up by the timer counter.

Pins  $P2_0$  and  $P2_1$  output the Od and R/W signals with the mode register RC.

#### P30 to P32 (Input/Output)

The  $P3_0$  to  $P3_2$  pins are I/O pins which are connected to the positive supply with pull-up resistors. These pins can be set to I/O mode for use in a serial interface with the mode register RE.

#### SYSTEM CONFIGURATION

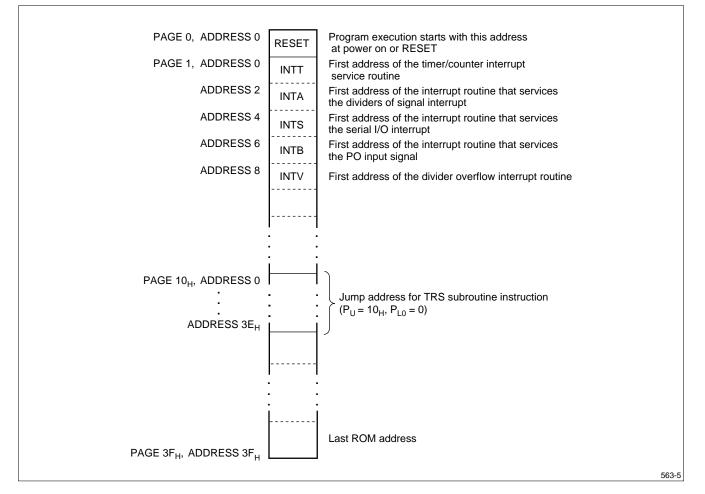

#### **ROM and Program Counter**

The on-chip ROM has a configuration of 64-page  $\times$  64-step  $\times$  8-bit, and stores programs and table data.

The program counter consists of a 6-bit page address counter  $\mathsf{P}_U$  and 6-bit binary counter  $\mathsf{P}_L$  used to specify the steps within a page.

The locations shown in Figure 3 are allocated in the on-chip ROM.

#### Stack Pointer (SP)

The stack pointer (SP) is an 8-bit shift register which holds the starting address of the stack area of RAM space. Immediately after the reset, the contents of the stack pointer are uninitialized and must be set to an appropriate value. If, for instance, the initial value of the stack pointer is set to  $80_{\text{H}}$ , the data memory is beginning with the highest address (excluding the display RAM area).  $7F_{\text{H}}$  is usable as a stack area.

#### RAM

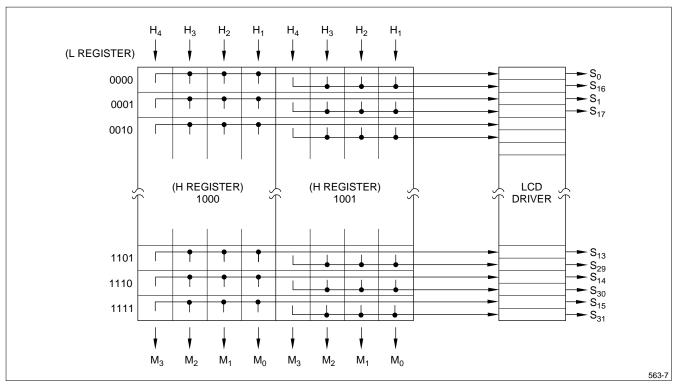

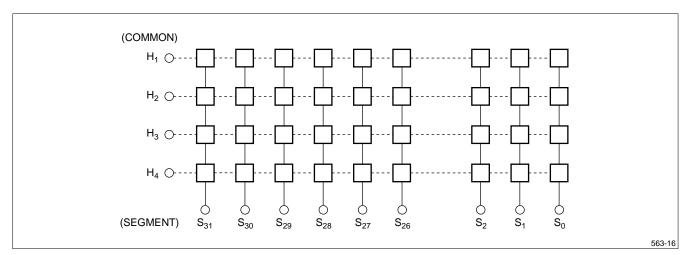

Data memory has a 160-word × 4-bit configuration, and is used to store processing data and other information. Data memory is also used as a stack area to save register values, the program counter value and program status word (PSW) at the time a subroutine jump or an interrupt occurs. Figure 4 shows the RAM configuration. 2 x 16 x 4-bit of entire RAM space is used as a display RAM area from which data is output to LCD segment driving pins. A LCD with a 1/4 duty and 1/3 bias format can be directly driven by writing display data into the display RAM area. The display RAM outputs are, as shown in Figure 5, connected to segment output pins S<sub>0</sub> to S<sub>31</sub> for individual set of common outputs H<sub>1</sub> to H<sub>4</sub>. The segment output pins provide a single digit of display RAM data M<sub>0</sub> to M<sub>3</sub>, as a LCD driving waveform signal according to H<sub>1</sub> to H<sub>4</sub> outputs. The operations of the display RAM are identical to those of other RAM areas.

Figure 4. Program ROM Map

| 5    |      |      |      |      |      |      |      |      |                 |                 |

|------|------|------|------|------|------|------|------|------|-----------------|-----------------|

| LH   | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000            | 1001            |

| 0000 |      |      |      |      |      |      |      |      | S <sub>0</sub>  | S <sub>16</sub> |

| 0001 |      |      |      |      |      |      |      |      | S <sub>1</sub>  | S <sub>17</sub> |

| 0010 |      |      |      |      |      |      |      |      | S <sub>2</sub>  | S <sub>18</sub> |

| 0011 |      |      |      |      |      |      |      |      | S <sub>3</sub>  | S <sub>19</sub> |

| 0100 |      |      |      |      |      |      |      |      | $S_4$           | S <sub>20</sub> |

| 0101 |      |      |      |      |      |      |      |      | $S_5$           | S <sub>21</sub> |

| 0110 |      |      |      |      |      |      |      |      | $S_6$           | S <sub>22</sub> |

| 0111 |      |      |      |      |      |      |      |      | S <sub>7</sub>  | S <sub>23</sub> |

| 1000 |      |      |      |      |      |      |      |      | S <sub>8</sub>  | S <sub>24</sub> |

| 1001 |      |      |      |      |      |      |      |      | S <sub>9</sub>  | S <sub>25</sub> |

| 1010 |      |      |      |      |      |      |      |      | S <sub>10</sub> | S <sub>26</sub> |

| 1011 |      |      |      |      |      |      |      |      | S <sub>11</sub> | S <sub>27</sub> |

| 1100 |      |      |      |      |      |      |      |      | S <sub>12</sub> | S <sub>28</sub> |

| 1101 |      |      |      |      |      |      |      |      | S <sub>13</sub> | S <sub>29</sub> |

| 1110 |      |      |      |      |      |      |      |      | S <sub>14</sub> | S <sub>30</sub> |

| 1111 |      |      |      |      |      |      |      |      | S <sub>15</sub> | S <sub>31</sub> |

**NOTE:** The area with the thick is allocated for a display RAM and the Sn (n = 0 to 31) shows the related segment outputs.

Figure 5. RAM Configuration

Figure 6. Display RAM and Its LCD Segment Outputs

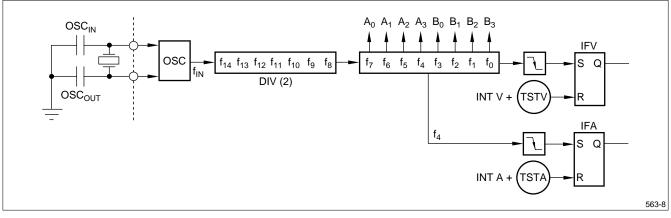

Figure 7. Real-Time Clock Divider

# Accumulator (A), Subaccumulator (B) and Arithmetic and Logic Unit (ALU)

The accumulator (A) is a 4-bit working register which is the nucleus of the single chip system. It holds the results of operations and transfers data to memory, I/O ports and registers.

A subaccumulator (B) is another 4-bit register. It is used as one of the general purpose registers, and when combined with the A to form a B-A register pair, allows data transfer on an 8-bit basis.

The arithmetic and logic unit (ALU) performs, in conjunction with a carry flag (C), binary addition, shift operations and logical operations such as AND, OR, EX-OR and complement.

#### General Purpose Registers (H, L, D, E)

Registers H and L are 4-bit general purpose registers. They can transfer and compare data with the A on a 4-bit basis. Registers D and E are 4-bit registers and can transfer data with the H and L registers on an 8-bit basis. The H and L as well as the D and E registers can be combined into 8-bit register pairs, and can be used as pointers to data memory locations. The L register can be incremented or decremented and is used to access I/O ports and mode registers.

#### Clock Divider, IFV Flag, IFA Flag

The device contains a crystal oscillator and a 15stage divider as shown in Figure 6. A real-time clock can be provided by connecting an external crystal oscillator between the oscillator pins. When an external 32.768 kHz crystal oscillator is used, the  $f_0$  signal is a frequency of 1 Hz.

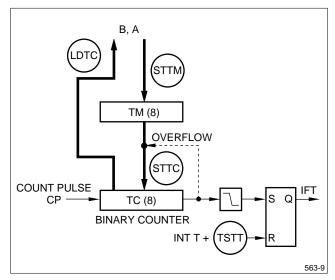

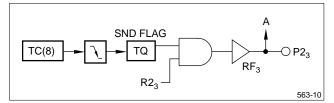

#### Timer/Counter and the SND Signal

The timer/counter consists of an 8-bit count register (TC) and an 8-bit modulo register (TM).

The count register is an 8-bit incremental binary counter. It is incremented by one at the falling edge of its count pulse (CP) input. If the count register overflows, the timer interrupt request flag IFT is set, and the contents of the modulo register (TM) are loaded into the count register (see Figure 7).

The count pulse Cp can be selected from divider signals  $f_{In}$ ,  $f_8$  and  $f_0$ , and the system clock, by using the mode register RD. If the count register (TC) overflows, the SND flag reverses its status at the falling edge of the TC. A sound signal can be obtained at the TC output by putting P2 in output mode and sending a '1' to pin P2<sub>3</sub> (see Figure 8).

Figure 8. Timer/Counter

Figure 9. SND Signal

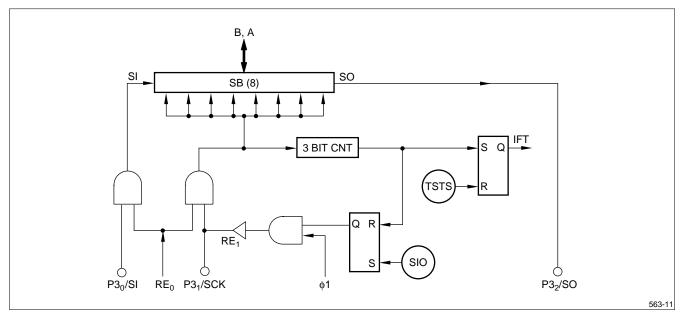

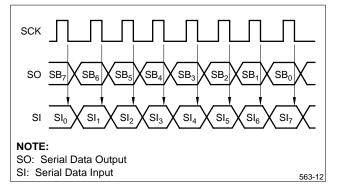

#### Serial Interface and IFS

The serial interface consists of an 8-bit shift register (SB) and a 3-bit counter, which is used to input and output the serial data. The serial clock can be selected with either an internal clock (system clock) or an external clock.

In serial shift operations, the highest bit data of the shift register (SB) is output from the SO pin, and the data input from the SI pin at the rising edge of a serial clock is loaded into the lowest bit of the shift register. When the internal clock is used, immediately after the SIO instruction is executed, the serial operation begins and stops with eight clocks which are output from the SCK pin. Upon completion of an 8-bit shift operation, the serial I/O ending flag IFS is set each time a 3-bit counter overflows, and an interrupt request occurs.

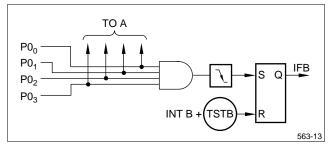

#### Input Port P0 and IFB Flag

The IFB flag is set at the falling edge of the signal applied to the input port P0 by which the interrupt is enabled.

When port P0 is used as a key input, it can cause an interrupt each time a key is operated.

Figure 10. Serial Interface

Figure 12. P0 Port

Figure 13. Interrupt Handling

| PORT | PORT FUNCTION                                                                            |                | DIRECT 4-BIT<br>PARALLEL I/O |               | OUT<br>JCTION   | BIT INDEPENDENT<br>OUTPUT SPN         |

|------|------------------------------------------------------------------------------------------|----------------|------------------------------|---------------|-----------------|---------------------------------------|

| PORT | FUNCTION                                                                                 | INPUT<br>(INA) | OUTPUT<br>(OUTA)             | INPUT<br>(IN) | OUTPUT<br>(OUT) | DIRECT PIN-<br>INDEPENDENT OUTPUT RPn |

| P0   | Input-only port                                                                          | 0              | Х                            | 0             | Х               | Х                                     |

| P1   | I/O port                                                                                 | 0              | 0                            | Х             | 0               | 0                                     |

| P2   | I/O port, P2 <sub>3</sub> sound output                                                   | 0              | 0                            | Х             | Х               | 0                                     |

| P3   | P3 <sub>0</sub> - SI, P3 <sub>1</sub> - SCK, P3 <sub>2</sub> - SO,<br>multi-control port | 0              | 0                            | Х             | Х               | 0                                     |

NOTE: O - Yes, X - No

#### Interrupts

When an interrupt occurs, the corresponding interrupt request flag is set. The CPU acknowledges the interrupt if it is enabled (master interrupt enable flag and the corresponding interrupt enable flag are set). If more than one interrupt occurs simultaneously, all of the corresponding interrupt request flags will be set, but the CPU will only acknowledge that interrupt with the highest priority and other interrupts will be queued

#### I/O Ports

Port P0 is a 4-bit parallel input port. The IFB flag is set at the falling edge of this port.

Port P1 can be switched between input and output modes, 4-bits at a time.

Each bit of port P2 can be independently placed in input or output mode by setting the corresponding bit of mode register RF.

Ports  $P2_0$  and  $P2_1$  can output the OD and R/W signals, respectively. In those cases, these pins should be

kept HIGH in an output mode. Port  $P2_3$  outputs the SND signal in the output mode.

Port P3 is a 4-bit I/O port which can be placed in input or output mode, 3-bits at a time. Each bit of port P3 can be set the I/O modes (SI, SO, SCK) of a serial interface.

Ports P1 and P3 are placed in an output mode when a port output instruction is executed, and in an input mode when a port input instruction is executed. After an ACL operation, ports P1, P2 and P3 are all placed in an input mode.

Every input port has pull-up resistors. (Pull-up resistors for I/O ports are effective only when the ports are placed in an input mode.)

Ports P1 through P3 in an output mode can be independently set or reset by instructions.

When a key-matrix is configured by using I/O ports, a multiple key depression may cause a short to occur. To prevent this from occuring, port P1 should be used an an output.

#### **Standby Mode**

Executing the CEND instruction places the device in standby mode. To reduce power consumption, the system clock is inactivated. Standby mode may be cleared with the interrupt request or the RESET signal.

#### **Reset Function (ACL)**

Applying a LOW level signal to the RESET pin resets the internal logic of the device and applying a HIGH level signal starts execution of the program at address 0, page 0. Once the device is reset, all I/O ports are placed in input mode, all interrupts are disabled, and the LCD display turns off. The device is also reset when it is powered up.

#### **Main Clock Oscillation Circuit**

The main clock oscillator requires an external resistor across pins  $CK_1$  and  $CK_2$ . Instead of using on-chip oscillator, an external clock may be applied to pin  $CK_1$ . In this case, pin  $CK_2$  should be left open. The system clock  $\phi$  is a divided clock equivalent to 1/4 of the clock applied to pin  $CK_1$ .

#### **LCD** Driver

#### **Display Segment**

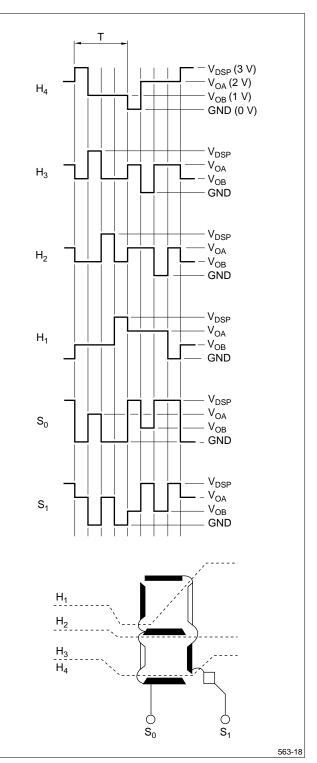

The SM563 contains an on-chip LCD driver which can directly drive a LCD with a 1/4 duty and 1/3 bias. Figure 14 shows an example of LCD segment configuration for 1/4 duty.

Each segment of the LCD can be turned on or off by software control of the setting of the corresponding bit '1' or '0' in the display RAM area (see Figure 4).

The LCD digit may have any shape, provided that the maximum number of segments does not exceed 128 (see Figure 15). Figure 14 shows an example of a 7-segment numeric LCD digit.

Figure 14. Main Clock Sources

Figure 15. 7-Segment Numeric LCD Digit

Figure 16. LCD Segment Configuration for 1/4 Duty

#### LCD Driving Signal Waveform

Figure 16 shows the LCD signal driving waveforms required to display the number '5' on the 7-segment display shown in Figure 14 (segment outputs  $S_0$  and  $S_1$  are used). A voltage of 3 V is applied to pin  $V_{DSP}$  in Figure 16. The frame frequency (I/T) can be selected from 64 Hz or 128 Hz by mask options.

#### $V_{\text{OA}}$ and $V_{\text{OB}}$

The device contains bleeder resistors to allow 1/3 bias driving. When V<sub>DSP</sub> is 3 V, voltages of 2 V and 1 V are output from pins V<sub>OA</sub> and V<sub>OB</sub> respectively. Normally pins V<sub>OA</sub> and V<sub>OB</sub> are left open. When an LCD with a large display area is driven, connect capacitors across pins V<sub>OA</sub> and V<sub>DSP</sub>, and across V<sub>OB</sub> and V<sub>DSP</sub> to improve the rise time of the LCD driving signal.

#### **INSTRUCTION SET**

#### **ROM Address Instructions**

| MNE-<br>MONIC       | MACHINE<br>CODE    | OPERATIONS                                                                                                                                            |

|---------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| TR x                | 80 - BF            | $P_L \gets x \ (I_5 - I_0)$                                                                                                                           |

| TL xy<br>(2-byte)   | E0 - EF<br>00 - FF | $\begin{array}{l} P_{U} \gets x \; (I_{11} - I_6) \\ P_{L} \gets y \; (I_5 - I_0) \end{array}$                                                        |

| TRS x               | C0 - DF            | $\begin{array}{l} (SP-2),(SP-3),(SP-4)\leftarrow PC\\ SP\leftarrow SP-4\\ P_U\leftarrow 10_H\\ P_L\leftarrow x(I_4,I_3,I_2,I_1,I_0,O) \end{array}$    |

| CALL xy<br>(2-byte) | F0 - FF<br>00 - FF | $\begin{array}{l} (SP-2),(SP-3),(SP-4)\leftarrow PC\\ SP\leftarrow SP-4,P_U\leftarrow x(I_{11}-I_6)\\ P_L\leftarrow y(I_5-I_0) \end{array}$           |

| JBA x<br>(2-byte)   | 7F<br>30 - 3F      | $\begin{array}{l} P_{U5},-P_{U2} \leftarrow x \; (I_3 - I_0) \\ P_{U1},P_{U0},P_{L5},P_{L4} \leftarrow B \\ P_{L3} - P_{L0} \leftarrow A \end{array}$ |

| RTN                 | 61                 | $P_{U},P_{L} \leftarrow (SP),(SP+1),(SP+2)$                                                                                                           |

| RTNS                | 62                 | $\begin{array}{l} P_{U},  P_{L} \leftarrow (SP),  (SP+1),  (SP+2), \\ SP \leftarrow SP+4 \end{array}$                                                 |

| RTNI                | 63                 | $\begin{array}{l} P_{U},  P_{L} \leftarrow (SP),  (SP+1),  (SP+2), \\ PSW \leftarrow (SP+3),  SP \leftarrow SP+4 \\ IME \leftarrow 1 \end{array}$     |

#### **RAM Address Instructions**

| MNE-<br>MONIC       | MACHINE<br>CODE | OPERATIONS                                                 |

|---------------------|-----------------|------------------------------------------------------------|

| STL                 | 69              | $L \leftarrow A$                                           |

| STH                 | 68              | $H \leftarrow A$                                           |

| EXHD                | 3F              | $H \leftrightarrow D, L \leftrightarrow E$                 |

| LIHL xy<br>(2-byte) | 3D<br>00 - FF   | $H \leftarrow (I_7 - I_4),  L \leftarrow y \; (I_3 - I_0)$ |

Figure 17. LCD Driving Signal Waveform (Required to Display the Number 5)

# **Data Transfer Instructions**

| MNE-<br>MONIC       | MACHINE<br>CODE | OPERATIONS                                                                                                                                                                                                                                        |

|---------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EX pr               | 5C - 5F         | $A \leftrightarrow (pr)$                                                                                                                                                                                                                          |

| LDX adr<br>(2-byte) | 7D<br>00 - FF   | $A \leftarrow (adr)$                                                                                                                                                                                                                              |

| STX adr<br>(2-byte) | 7E<br>00 - FF   | $(adr) \leftarrow A$                                                                                                                                                                                                                              |

| EXX adr<br>(2-byte) | 7C<br>00 - FF   | $A \leftrightarrow (adr)$                                                                                                                                                                                                                         |

| LAX x               | 10 - 1F         | $A \gets x \; (I_3 - I_0)$                                                                                                                                                                                                                        |

| LIBA xy<br>(2-byte) | 3C<br>00 - FF   | $\begin{array}{l} B \leftarrow x \; (I_7 - I_4) \\ A \leftarrow y \; (I_3 - I_0) \end{array}$                                                                                                                                                     |

| LBAT                | 60              | $\begin{array}{l} \textbf{B} \leftarrow \textbf{ROM} \; (\textbf{P}_{U5} - \textbf{P}_{U2},  \textbf{B},  \textbf{A})_{H} \\ \textbf{A} \leftarrow \textbf{ROM} \; (\textbf{P}_{U5} - \textbf{P}_{U2},  \textbf{B},  \textbf{A})_{L} \end{array}$ |

| LDL                 | 65              | $A \leftarrow L$                                                                                                                                                                                                                                  |

| LD pr               | 54 - 57         | $A \leftarrow (pr)$                                                                                                                                                                                                                               |

| ST pr               | 58 - 5B         | $(pr) \leftarrow A$                                                                                                                                                                                                                               |

| EXH                 | 6C              | $A \leftrightarrow H$                                                                                                                                                                                                                             |

| EXL                 | 6D              | $A \leftrightarrow L$                                                                                                                                                                                                                             |

| EXB                 | 6E              | $A \leftrightarrow B$                                                                                                                                                                                                                             |

| STB                 | 6A              | $B \gets A$                                                                                                                                                                                                                                       |

| LDB                 | 66              | $A \gets B$                                                                                                                                                                                                                                       |

| LDH                 | 64              | $A \gets H$                                                                                                                                                                                                                                       |

| PSHBA               | 28              | $\begin{array}{l} (SP-1) \leftarrow B,  (SP \leftarrow 2) \leftarrow A, \\ SP \leftarrow SP - 2 \end{array}$                                                                                                                                      |

| PSHHL               | 29              | $\begin{array}{l} (SP-1) \leftarrow H,  (SP \leftarrow 2) \leftarrow L, \\ SP \leftarrow SP -2 \end{array}$                                                                                                                                       |

| РОРВА               | 38              | $B \leftarrow (SP + 1), A \leftarrow (SP), SP \leftarrow SP + 2$                                                                                                                                                                                  |

| POPHL               | 39              | $\begin{array}{l} H \leftarrow (SP+1), L \leftarrow (SP), \\ SP \leftarrow SP+2 \end{array}$                                                                                                                                                      |

| STSB                | 70              | $SB_{H} \leftarrow B, SB_{L} \leftarrow A$                                                                                                                                                                                                        |

| STSP                | 71              | $SP_{H} \leftarrow B, SP_{L} \leftarrow A$                                                                                                                                                                                                        |

| STTC                | 72              | $TC \gets TM$                                                                                                                                                                                                                                     |

| STTM                | 73              | $TM_{H} \leftarrow B, TM_{L} \leftarrow A$                                                                                                                                                                                                        |

| LDSB                | 74              | $B \leftarrow SB_H, A \leftarrow SB_L$                                                                                                                                                                                                            |

| LDSP                | 75              | $B \leftarrow SP_H, A \leftarrow SP_L$                                                                                                                                                                                                            |

| LDTC                | 76              | $B \leftarrow TC_H, A \leftarrow TC_L$                                                                                                                                                                                                            |

| LDDIV               | 77              | $B \gets DIV_H, A \gets DIV_L$                                                                                                                                                                                                                    |

### **Arithmetic Instructions**

| MNE-<br>MONIC | MACHINE<br>CODE | OPERATIONS                                                                                                  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------|

| ADX x         | 00 - 0F         | $A \leftarrow A + x (I_3 - I_0)$ , Skip if $C_Y = 1$                                                        |

| ADD           | 36              | $A \leftarrow A + (HL)$                                                                                     |

| ADDC          | 37              | $\begin{array}{l} A \leftarrow A + (HL) + C,  C \leftarrow C_{Y} \\ Skip \text{ if } C_{Y} = 1 \end{array}$ |

| OR            | 31              | $A \leftarrow A \cup (HL)$                                                                                  |

| AND           | 32              | $A \gets A \cap (HL)$                                                                                       |

| EOR           | 33              | $A \leftarrow A \oplus (HL)$                                                                                |

| ANDB          | 22              | $A \leftarrow A \cap B$                                                                                     |

| ORB           | 21              | $A \leftarrow A \cup B$                                                                                     |

| EORB          | 23              | $A \gets A \oplus B$                                                                                        |

| COMA          | 6F              | $A \leftarrow \overline{A}$                                                                                 |

| ROTR          | 25              | $C \to A_3 \to A_2 \to A_1 \to A_0 \to C$                                                                   |

| ROTL          | 35              | $C \gets A_3 \gets A_2 \gets A_1 \gets A_0 \gets C$                                                         |

| INCB          | 52              | $B \leftarrow B + 1$ , Skip if $B = F_H$                                                                    |

| DECB          | 53              | $B \leftarrow B - 1$ , Skip if $B = 0$                                                                      |

| INCL          | 50              | $L \leftarrow L + 1$ ,Skip if $L = F_H$                                                                     |

| DECL          | 51              | $L \leftarrow L - 1$ , Skip if $L = 0$                                                                      |

| DECM<br>adr   | 79<br>00 - FF   | $(adr) \leftarrow (adr) - 1$ , Skip if $(adr) = 0$                                                          |

| INCM<br>adr   | 78<br>00 - FF   | $(adr) \leftarrow (adr) + 1$ , Skip if $(adr) = F_H$                                                        |

# **Test Instructions**

| MNE-<br>MONIC | MACHINE<br>CODE | OPERATIONS                          |

|---------------|-----------------|-------------------------------------|

| ТАМ           | 30              | Skip if A = (HL)                    |

| ТАН           | 24              | Skip if A = H                       |

| TAL           | 34              | Skip if A = L                       |

| TAB           | 20              | Skip if A = B                       |

| TC            | 2A              | Skip if C = 0                       |

| TM x          | 48 - 4B         | Skip if (HL)x = 1                   |

| TA x          | 4C - 4F         | Skip if Ax = 1                      |

| TSTT          | 2B              | Skip if IFT = 1, IFT $\leftarrow 0$ |

| TSTA          | 2C              | Skip if IFA = 1, IFA $\leftarrow 0$ |

| TSTS          | 2D              | Skip is IFS = 1, IFS $\leftarrow 0$ |

| TSTB          | 2E              | Skip if IFB = 1, IFB $\leftarrow 0$ |

| TSTV          | 2F              | Skip if IFV = 1, IFV $\leftarrow 0$ |

#### **Bit Manipulation Instructions**

| MNE-<br>MONIC    | MACHINE<br>CODE | OPERATIONS                  |

|------------------|-----------------|-----------------------------|

| SM x             | 40 - 43         | $(HL)x \leftarrow 1$        |

| RM x             | 44 - 47         | $(HL)x \leftarrow 0$        |

| RC               | 26              | $C \leftarrow 0$            |

| SC               | 27              | $C \leftarrow 1$            |

| RIME             | 3A              | $IME \leftarrow 0$          |

| SIME             | 3B              | $IME \leftarrow 1$          |

| DI x<br>(2-byte) | 7F<br>C0 - DF   | $IEF \leftarrow IEF \cap X$ |

| El x<br>(2-byte) | 7F<br>E0 - FF   | IEF ∪ x                     |

# **Special Instructions**

| MNE-<br>MONIC    | MACHINE<br>CODE | OPERATIONS         |

|------------------|-----------------|--------------------|

| SIO              | 3E              | Serial I/O start   |

| IDIV<br>(2-byte) | 7F<br>10        | $DIV \leftarrow 0$ |

| SKIP             | 00              | No operation       |

| CEND<br>(2-byte) | 7F<br>00        | System clock stop  |

NOTE: The machine code consists of 8-bits including I\_7, I\_6, I\_5, I\_4, I\_3, I\_2, I\_1 and I\_0

#### **I/O Instructions**

| MNE-<br>MONIC       | MACHINE<br>CODE | OPERATIONS                                                                        |

|---------------------|-----------------|-----------------------------------------------------------------------------------|

| IN                  | 67              | $A \leftarrow P0$                                                                 |

| OUT                 | 6B              | $P1 \gets A$                                                                      |

| INA x<br>(2-byte)   | 7F<br>A0 - A9   | $A \gets P(x),  R(x)$                                                             |

| OUTA<br>(2-byte)    | 7F<br>B0 - BF   | $P(x),R(x)\leftarrowA$                                                            |

| INBA x              | 7F<br>80 - 82   | $\begin{array}{l} B \leftarrow R \; (x + 1) \\ A \leftarrow R \; (x) \end{array}$ |

| OUTBA x<br>(2-byte) | 7F<br>90 - 93   | $ \begin{array}{l} R \; (x+1) \leftarrow B \\ R \; (x) \leftarrow A \end{array} $ |

| SP xy<br>(2-byte)   | 7A<br>00 - F3   | $P\left(y\right) \gets P\left(y\right)x$                                          |

| BP xy<br>(2-byte)   | 7B<br>00 - F3   | $P\left(y\right) \gets P\left(y\right)x$                                          |

| RDS<br>(2-byte)     | 7F<br>60        | DS ← 0                                                                            |

| RBR<br>(2-byte)     | 7F<br>70        | $BR \leftarrow 0$                                                                 |

| SDS<br>(2-byte)     | 7F<br>61        | DS ← 1                                                                            |

| SBR<br>(2-byte)     | 7F<br>71        | BR ← 0                                                                            |

| READ<br>(2-byte0    | 7F<br>62        | $A \leftarrow P4$ with OD                                                         |

| WRIT<br>(2-byte)    | 7F<br>72        | $P4 \leftarrow A$ with R/W                                                        |

| READB<br>(2-byte)   | 7F<br>63        | $A \leftarrow P4$ , with OD<br>$B \leftarrow P5$                                  |

| WRITB<br>(2-byte)   | 7F<br>73        | $P4 \leftarrow A$ , with R/W<br>$P5 \leftarrow B$                                 |

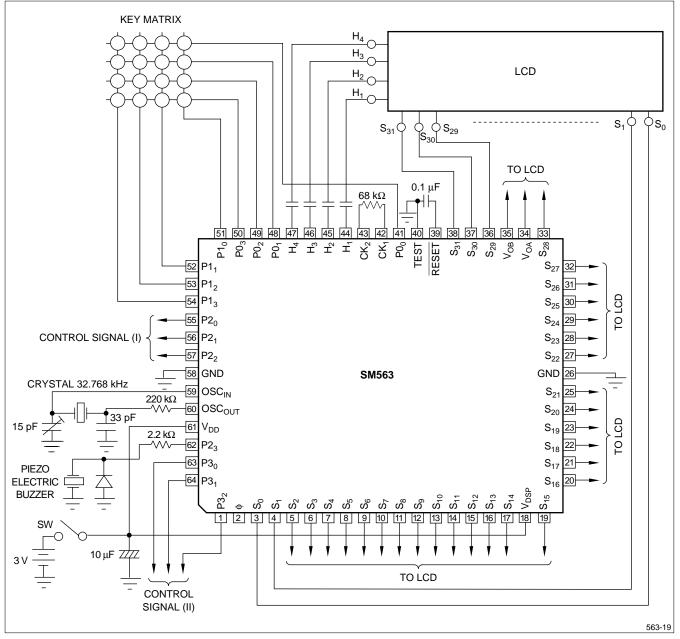

#### SYSTEM CONFIGURATION EXAMPLE

Figure 18. Example of a Home Security System

#### LIFE SUPPORT POLICY

SHARP components should not be used in medical devices with life support functions or in safety equipment (or similiar applications where component failure would result in loss of life or physical harm) without the written approval of an officer of the SHARP Corporation.

#### LIMITED WARRANTY

SHARP warrants to its Customer that the Products will be free from defects in material and workmanship under normal use and service for a period of one year from the date of invoice. Customer's exclusive remedy for breach of this warranty is that SHARP will either (i) repair or replace, at its option, any Product which fails during the warranty period because of such defect (if Customer promptly reported the failure to SHARP in writing) or, (ii) if SHARP is unable to repair or replace, refund the purchase price of the Product upon its return to SHARP. This warranty does not apply to any Product which has been subjected to misuse, abnormal service or handling, or which has been altered or modified in design or construction, or which has been serviced or repaired by anyone other than Sharp. The warranties set forth herein are in lieu of, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will Sharp be liable, or in any way responsible, for any incidental or consequential economic or property damage.

The above warranty is also extended to Customers of Sharp authorized distributors with the following exception: reports of failures of Products during the warranty period and return of Products that were purchased from an authorized distributor must be made through the distributor. In case Sharp is unable to repair or replace such Products, refunds will be issued to the distributor in the amount of distributor cost.

SHARP reserves the right to make changes in specifications at any time and without notice. SHARP does not assume any responsibility for the use of any circuitry described; no circuit patent licenses are implied.

# SHARP.

#### NORTH AMERICA

SHARP Microelectronics of the Americas 5700 NW Pacific Rim Blvd., M/S 20 Camas, WA 98607, U.S.A. Phone: (360) 834-2500 Telex: 49608472 (SHARPCAM) Facsimile: (360) 834-8903 http://www.sharpsma.com

#### EUROPE

SHARP Electronics (Europe) GmbH Microelectronics Division Sonninstraße 3 20097 Hamburg, Germany Phone: (49) 40 2376-2286 Telex: 2161867 (HEEG D) Facsimile: (49) 40 2376-2232

#### ASIA

SHARP Corporation Integrated Circuits Group 2613-1 Ichinomoto-Cho Tenri-City, Nara, 632, Japan Phone: (07436) 5-1321 Telex: LABOMETA-B J63428 Facsimile: (07436) 5-1532